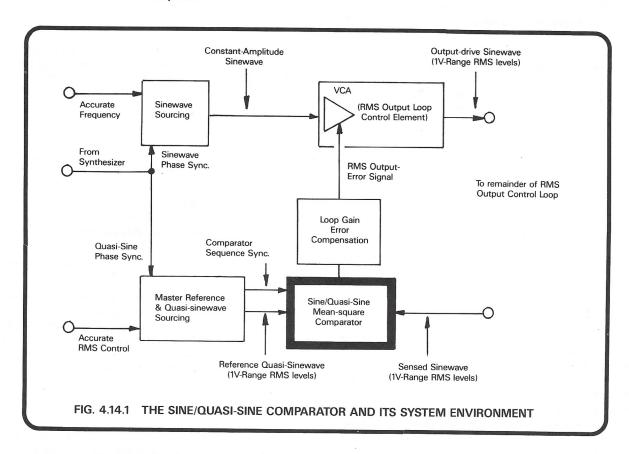

The circuits described in this section perform the following functions:

- Connect the VCA output to the terminals to provide the basic 1V range:

0.09V to 2V

- (2) Amplify the VCA output voltages to the instrument's terminals, for the 10V range: 0.9V to 20V

- (3) Attenuate basic 1V range voltages to provide the millivolt ranges:

9mV to 200mV on 100mV Range 0.9mV to 20mV on 10mV Range  $90\mu$ V to 2mV on 1mV Range

- (4) Sense the voltages at the output terminals (or at the load in Remote Sense) and scale the signal to the 1V RMS Full-Range level for comparison with the quasi-sinewave.

- (5) Provide switching of AC voltage output, Range, Guard and Sense, under the control of signals from the Analog Control Interface.

- (6) Detect excess currents in the output circuit, providing a status signal to the CPU via the Analog Control Interface.

- (7) Detect excess voltages on the PHi (I+) output line, providing a status signal to the CPU via the Analog Control Interface.

The circuits in this section are located as follows:

Millivolt attenuator and sense circuitry:

AC Assembly

Power amplification:

Power Amplifier Assembly.

Output control:

Output Control Assembly.

Terminals:

- Mother Assembly.

- Terminal Board.

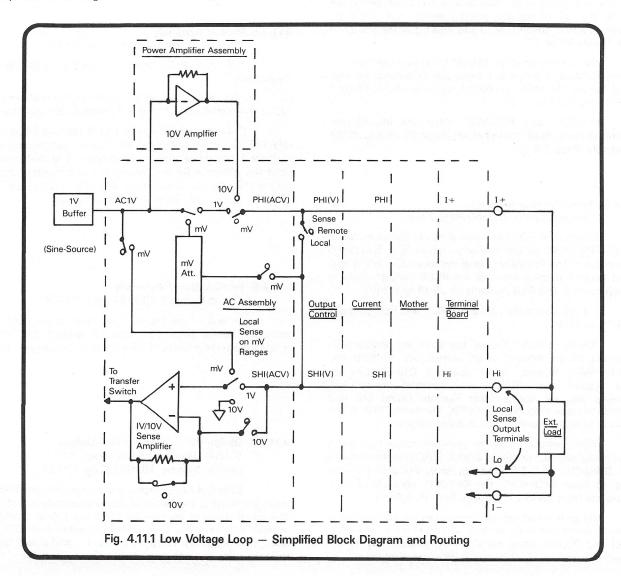

A simplified block diagram of the low voltage loop and routing appears in Fig. 4.11.1.

### 4.11.1 General

This description follows the 1V range path from the VCA buffer to the Sine/Quasi-Sine Comparator (at the input of the transfer switch M16). The 10V and millivolt output and sense conditioning are included.

On the circuit diagrams, the relay contacts are shown in the un-energized condition.

For High Voltage output and sense conditioning see Sections 4.12 and 4.13.

### 4.11.2 1V Loop — Power Delivery

### 4.11.2.1 Sine-Source Assembly

(Circuit diagram 430446 Page 7.6-3)

The 1V Buffer (page 7.6-3) is described in Sect 4.10, as part of the output amplitude control circuitry. Its output voltage, signal 'AC 1V' ranging between 0.9V to 2V RMS; is fed out of the Sine-Source assembly on J6-41, via the Mother assembly, and input to the AC assembly on J7-41 (page 7.7-1).

### 4.11.2.2 AC Assembly

(Circuit diagram 430447 Page 7,7-1)

With the 1V Range selected, relays RL7 (1V) and RL19 ( $\overline{1}\overline{kV}$ ) are closed, and relays RL4, 5, 6, 17, 18 and 20 are open. So the AC 1V signal is passed directly out of the AC assembly, via RL7, fuse F1, RL19 and fuse F2 as the Power-Hi signal 'PHI(ACV)' at J7-27.

The power common 'PLO(ACV)' is derived from the in-guard Common-2 supply at the star-point Common-2B, and passed out via the three energized contacts of AC Voltage selector relay RL10 to J7-31.

PHI(ACV) and PLO(ACV) travel via the Mother assembly to the Output Control assembly at J5-25 and J5-29 respectively (Page 7.5-1).

### 4.11.2.3 Output Control Assembly

(Circuit diagram 430550 Page 7.5-1)

In normal 4-wire operation (Remote Sense selected) with OUTPUT 'ON' on the 1V Range, relays RL3, 4, 5 and 6 are energized. The PHI(ACV) signal bypasses the 1kV Range output current sensing resistors via RL1-6 contact, passing through fuse F3 and RL6 contacts to J5-19 as PHI(V).

PLO(ACV) travels via F2, F1, RL3 and RL5 contacts to J5-23 as PLO(V).

The front panel 'Guard' terminals are permanently connected to the internal guard shields via J5-15/16 and J5-11/12. With 'Remote Guard' selected, C19 isolates the guard system from PLO(V) (I – terminal connection), bypassing any HF spikes. With Remote Guard off, RL7 connects the guards to PLO(V) via PTC thermistor R40, which assists in reducing noise on the millivolt ranges.

With Remote Sense not selected, relays RL3 and 4 are un-energized. RL4 contacts short PHI(ACV) to the sense Hi input SHI(ACV). RL3-2/8 contacts short PLO(ACV) to the sense Lo input SLO(ACV); the RL3-5/11 contacts disconnecting the front panel I- terminal from PLO(ACV).

As with all voltage and current ranges, connection to the front panel terminals is through the Current assembly. PHI(V) and PLO(V) travel via the Mother assembly to the Current assembly at J8-25 and J8-29 respectively.

### 4.11.2.4 Current Assembly

(Circuit Diagram 430555 page 7.8-1)

With any Voltage Range selected, relays RL8 and 9 are un-energized as shown. RL23 is energized; connecting PHI(V) to J8-8/9 as 'PHI' and PLO(V) to J8-16/17 as 'PLO'.

PHI and PLO then pass into the Mother assembly.

If the Current option is not fitted, a Link PCB (part No. 410182) is fitted in its place. This shorts:

J8-25 - PHI(ACV) to J8-8/9 - PHI,

J8-29 - PLO(ACV) to J8-16/17 - PLO.

The connections do not involve relay switching.

### 4.11.2.5 Mother Assembly

(Circuit Diagram 430532 page 7.16-1)

$\,$  PHI and PLO enter at J8-8/9 and J8-16/17 respectively.

PLO passes through the common mode choke L1 via J23-3 and J26-4 as  $^{\prime}I-^{\prime}$  to the Terminal Board assembly.

PHI is switched by relay RL1. If Remote Sense is not selected, RL1 is un-energized as shown; disconnecting PHI from the I + terminal circuit, and shorting it to the sense SHI input line. When in Remote Sense RL1 is energized, and PHI passes through the common mode choke L1 via J23-1 and J26-1 as 'I+' to the Terminal Board assembly.

### 4.11.2.6 Terminal Board Assembly

(Circuit Diagram 430634 page 7.17-3)

$\rm I+$  and  $\rm I-$  are filtered and passed to the front panel terminals. Ferrite bead FB1 and C2 protect the internal circuitry from the effects of HF pickup in the external circuit.

### 4.11.2.7 Option 42 — Rear Terminal Output

(Circuit Diagram 430530 page 7.17-1 Layout Drawing 480603 page 7.19-2)

Option 42 is incorporated at manufacture. With rear output terminals, the Terminal Board assembly is not fitted. The connections to the rear are taken fro J26 on the Mother assembly. A capacitor C1 connects Guard to Earth (Ground), and ferrite beads are fitted on the Hi, I + and Guard leads at the terminals. The mV range filter relay is not fitted.

### 4.11.3.1 Terminal Board Assembly

(Circuit Diagram 430634 page 7.17-3)

For the users with Option 42- Rear Output, the circuitry at the terminals is changed. Refer to sect. 4.11.2.7.

If Remote Sense is selected, the front panel sense terminals Hi and Lo are connected externally to  $\rm I+$  and  $\rm I-$  respectively, at the load.

The sensed voltage is filtered by FB2 and C3 to remove external HF pickup. This rejection is augmented by C1 for the millivolt ranges and for 'AC Zero' output selection. A signal ('R-', 'R+'), originating as 'TERM FILTER' in the Reference Divider, operates relay RL1 on the millivolt ranges. (Circuit Diagram 430535 page 7.4-4).

The filtered sense voltage is fed into the Mother assembly between J26-2 (HI) and J26-5 (LO). (No external sensing is provided for the millivolt ranges. See para 4.11.5 and Fig. 4.11.1 for the local sensing arrangement.)

### 4.11.3.2 Mother Assembly

(Circuit Diagram 430532 page 7.16-1)

LO passes through the common mode choke and directly to the Current assembly at J8-18 as SLO.

HI also passes through the choke and enters the Current assembly as SHI at J8-10. However, if Remote Sense is not selected, it is shorted to PHI by relay RL1. RL1 is energized from the REM SENSE  $\,+\,$  and  $\,-\,$  lines from the Output Control assembly.

### 4.11.3.3 Current Assembly

(Circuit Diagram 430555 page 7.8-1)

With any Voltage Range selected, relays RL8 and 9 are un-energized as shown. RL23 is energized; connecting SHI into the Mother assembly as 'SHI(V)' via J8-26, and SLO via J8-30 as 'SLO(V)'.

If the Current option is not fitted, the Link PCB shorts:

J8-10 - SHI to J8-26 - SHI(V),J8-18 - SLO to J8-30 - SLO(V).

The connections do not involve relay switching.

### 4.11.3.4 Output Control Assembly

(Circuit Diagram 430550 page 7.5-1)

In normal 4-wire operation (Remote Sense selected) with OUTPUT 'ON' on the 1V Range, relays RL3, 4, 5 and 6 are energized. SHI(V) enters from the Mother assembly at J5-20 and is passed directly through RL6 contacts (OUTPUT ON) and out via J5-26 as SHI(ACV).

$\mbox{SLO}(\mbox{V})$  travels via RL5 contacts (OUTPUT ON) to J5-30 as SLO(ACV).

With Remote Sense not selected, relays RL3 and 4 are un-energized. RL4 contacts short SHI (ACV) to the power Hi output PHI(ACV). RL3-2/8 contacts short SLO(ACV) to the power Lo output PLO(ACV).

SHI(ACV) and SLO(ACV) travel via the Mother assembly to the AC assembly at J7-28 and J7-32 respectively (Page 7.7-1).

### 4.11.3.5 AC Assembly

(Circuit Diagram 430447 page 7.7-1)

SLO(ACV) passes via the energized contact of the AC Voltage selector relay RL10, to be referred to the Sense Amplifier common 'SIG LO'.

With the IV Range selected, relay RL19 ( $\overline{1kV}$ ) contacts are closed, so SHI(ACV) appears at RL19-11 as 'SENSE HI' (Refer to the circuit diagram on page 7.7-2).

With the 1V Range selected, relay RL8 (1V) is energized, thus SENSE HI is applied to the non-inverting input of the Sense Amplifier via R126. RL14 is un-energized as shown, so the inverting input via R115 is referred to SIG LO.

RL3  $\overline{(100V+1kV)}$  is energized, connecting the Sense Amplifier output to the Sine/Quasi-Sine comparator transfer switch M16-11 (page 7.7-3).

A description of the Sense Amplifier appears in Section 4.11.4.

### 4.11.4 1V Sense Amplifier

(Circuit Diagram 430447 page 7.7-2)

The same amplifier is used on the 10V, 1V, 100mV, 10mV and 1mV Ranges. Its main purpose is to buffer the sense voltage, providing a high impedance input, low DC offset and flat frequency response.

On the 1V and millvolt ranges it is connected as a voltage-follower, sensing always being carried out at the 1V level. The 1V range sense signal originates at the load in Remote Sense, or in the Output Control assembly in local sense. For the millivolt ranges the 'AC1V' drive to the millivolt attenuators is sensed directly (see sect. 4.11.5).

On the 10V range an inverting configuration is employed. The circuit divides by 10, scaling the sense signal down to 1V range levels, for input to the Sine/Quasi-Sine comparator.

Separate arrangements are made for attenuation and scaling on the 100V and 1kV ranges. These are described in Section 4.13.

### 4.11.4.1 General

A discrete amplifier is used to provide the required slew rate up to 1MHz, all time constants being set well above 1MHz, with the first pole above 5MHz. It is configured into its follower circuit by relay switching.

Relays RL8, RL12 and RL3 are all energized on the 1V range. Relays RL11, RL13, RL14, RL15 and RL16 remain unenergized as shown in the diagram.

Dual JFET Q41 is a unity gain buffer in totem pole configuration. It drives the input protection diodes D37-D40, D44-D47, and the screen of Q40 inverting input; also driving the bootstrap buffer Q46. The total input capacitance is thus reduced to  $1\,-\,1.5$ pF.

The differential input amplifier, Dual FET Q40, has low input capacitance, and low input current. Q36 provides constant-current drive to Q40 and the bootstrapped followers Q38/Q39. R107 permits initial DC input-offset cancellation. The stage gain is low.

Emitter-followers Q34 and Q35 buffer the high-impedance low-gain FET stage, driving a differential signal into the high gain voltage amplifier Q29/Q30. This arrangement has the advantage of placing all the gain in one stage. The single-ended drive to Q31 output stage is taken from Q30 collector.

$\Omega$ 24 and  $\Omega$ 25 form a current mirror to equallize the collector currents of  $\Omega$ 29 and  $\Omega$ 30, preventing signal injection into the sense amplifier power rails.

L6 and L7 isolate the amplifier power rails from the 15V supply at HF. C50 is the main frequency-response compensation capacitor, providing smooth roll-off, with unity gain at around 5MHz.

On the IV Range, the output from Q31 is returned at low impedance, as 100% negative feedback to the amplifier input, via the closed contacts of RL12-8/14.

### 4.11.5 Millivolt Loop

(Circuit Diagram 430447 pages 4.7-1 and 4.7-2)

The basic 1V loop is extended by inserting a switched, passive, attenuator network. The switching circuit connects the selected millivolt output via RL19-11/8 directly to the SHI(ACV) line, not 'PHI'. Thus only the two front panel Sense Hi and Lo terminals are used to connect to the load.

The software forces Remote Sense OFF in the millivolt ranges. Except for a series resistor (R154) on the 1mV range, the AC1V signal is connected directly to the input of the Sense Amplifier at RL8-13. The Amplifier circuit remains

permanently in its non-inverting 1V configuration for all three millivolt ranges, so local sensing is carried out at 1V range levels.

Thus the output value at the terminals depends on both the calibrated value of the AC1V signal and the division ratio of the attenuator. In addition to the 1V range calibration, each millivolt range is also 'Autocalibrated' separately (refer to Section 1).

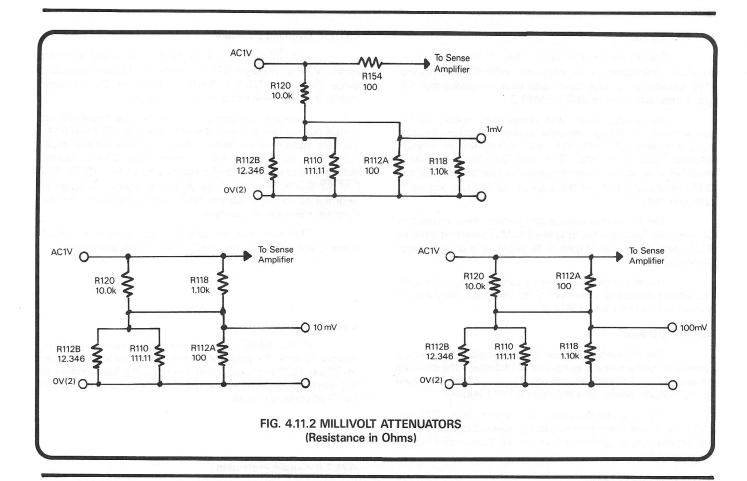

### **4.11.5.1 Millivolt Attenuators** (Fig. 4.11.2)

The AC1V signal is diverted from its 1V range route by the un-energized contacts of relay RL7. It is applied to the attenuator network via RL7-11.

The fixed chain (formed by R120 in series with the parellel combination of R112B and R110) is permanently connected between RL7-11 and the Common-2 star-point. Three levels of attenuation are achieved by switching R112A and R118. Relay RL5 is energized for the 10mV range only, RL6 for the 100mV range. The three arrangements are shown in Fig. 4.11.2.

On the 1mV range, the series resistor R154 is connected between RL7-11 and the Sense Amplifier input via RL11-5, but it is shorted on the 10mV and 100mV ranges by the closed contacts of RL5 and RL6 respectively.

Relay RL4 is energized on all millivolt ranges. The attenuator output is passed out to the SHI(ACV) line via RL4-8/9 and RL19-11/8. Capacitor C89 defines the specified bandwidth, filtering noise at HF.

### 4.11.6 10V Loop

(Circuit Diagrams: 430446 page 7.6-3, 430450 page 7.9-1 and 430447 page 7.7-1)

As noted in section 4.11.2, the 1V Buffer is part of the power delivery system for all ranges. On the 10V range its output (AC1V) passes via J6-41 from the Sine-Source assembly and into the Power Amplifier assembly (PA) at J9-36.

The AC1V signal is amplified by a factor of 10 in the inverting 10V Power Amplifier, whose output is switched onto the 'AC 10V  $\pm$  100V' line. This 10V range signal returns to the AC assembly at relay contacts RL17-13/4. It passes through RL19-2/5 to the PHI(ACV) line at J7-27.

The 10V range outputs then follow the same route (to and from the output terminals) as the 1V signals. Whether in Remote Sense or not, the sensed voltages return via the SHI(ACV) line to the same Sense Amplifier used for 1V range signals.

With 10V range selected, the sense amplifier has an inverting gain of O.1, returning the signal to the 1V levels required by the Sine/Quasi-Sine comparator.

### 4.11.7 10V Power Amplifier

(Circuit Diagram 430450 page 7.9-2)

The AC1V signal enters the PA assembly at J9-36, passing to the input of the 10V Power Amplifier via relays RL4-9/13 and RL3-9/13. It is referred to common 2B by developing a voltage across R124. The amplifier is best regarded as having separate DC and AC paths.

### 4.11.7.1 DC Path

The DC path is blocked by C56; M17 is the DC input amplifier, connected as an integrator with diode clamping. M19 operates as an inverter in open loop, so applies high DC gain to the output from M17 on M19-2.

The output from M19 drives both halves of the symmetrical, inverting, discrete power amplifier through current-limiters Q21 and Q24, and is buffered by emitter-followers Q22 and Q23. Q27 and Q29 form a voltage amplifier, driving the complementary output stage Q32 and Q33. R119 and R120 set the gain of the discrete stages to approximately 4.5.

The forward amplification contains three inversions, DC negative feedback being applied to M17 inverting input by R122, defining an overall gain of 10 in conjunction with input resistor R123.

The effect of the DC path is to sense and correct the DC offsets throughout the whole AC amplifier, referring the output to Common-2A at M17-3.

### 4.11.7.2 AC Path

The AC path is blocked by the integrator M17, but is applied to the non-inverting input of M19 through the blocking capacitor C56. M19 operates in open loop, applying its output to the discrete power amplifier (see 4.11.7.1 above).

The amplifier AC gain is also set to 10 by R122 and R123, the circuit time constants being selected to allow overall instrument output operation over the full frequency range of 10Hz to 1MHz.

### 4.11.7.3 Power Supplies

M17 and M19 are supplied from  $\pm\,15V$  common-2A rails, the discrete amplifier from the  $\pm\,38V$  supply, which is used solely for this purpose.

### 4.11.7.4 Overload Detection

The LIM ST line, connected to D74 anode, is pulled up to OV (in-guard logic-1) in the Reference Divider assembly (page 7.4-4) by AN2-9/1 (1MOhm). The Error OL message results from this line being driven to logic-Ø.

Overload detector Q31 reaches Vbe threshold on output current peaks, when the RMS value in R139 and R141 exceeds approximately 80mA. Similarly, Q34 detects peak currents in R147 and R149. In either case, Q34 conducts, pulling diodes D71 and D74 cathodes down to -15.7V. The LIM ST line is driven to logic-Ø, so the status message is returned to the CPU via the SSDA serial interface, and the Error OL message is displayed.

This does not preclude further increase in output current, but the accuracy specification is not guaranteed.

### 4.11.7.5 Overload Limiting

If the RMS output current increases to approximately 100mA, the peaks of current cause the Vbe threshold of Q28 or Q30 to be exceeded, shunting the base current of the corresponding voltage amplifier. Thus the output drive to the final stage is limited.

### 4.11.7.6 Output Protection

The output current passes through the combination of R144 and L8. At low frequencies the inductor provides a low output impedance, whereas at high frequencies the resistor stabilizes the amplifier when driving capacitive loads.

### 4.11.8 10V Sense Amplifier

(Circuit Diagram 430447 page 7.7-2)

The same amplifier is used on the 10V, 1V, 100mV, 10mV and 1mV Ranges. Its main purpose is to buffer the sense voltage, providing a high impedance input, low DC offset and flat frequency response.

On the 10V range an inverting configuration is employed. The circuit divides by 10, scaling the sense signal down to 1V range levels, for input to the Sine/Quasi-Sine comparator.

On the 1V and millivolt ranges it is connected as a voltage-follower. The millivolt ranges are simply the 1V range after passive attenuation, sensing always being carried out at the 1V level.

Separate arrangements are made for attenuation and scaling oin the 100V and 1kV ranges. These are described in Section 4.13.

### 4.11.8.1 General

A general description of the Sense Amplifier is given in Section 4.11.4.1 for the 1V range.

### 4.11.8.2 10V Range Configuration

On the 10V Range, relays RL14 and RL3 are both energized. Relays RL8, RL11, RL12, RL13, RL15 and RL16 remain un-energized as shown in the diagram.

The 'SENSE HI' signal is routed to the inverting input of the amplifier through the closed contacts of RL14 and resistor R115. With relays RL8 and RL11 not energized, the non-inverting input is referred to SIG LO.

The output from Q31 is returned via R121 as negative feedback to the amplifier input, the contacts of RL12-8/14 being open.

Thus the circuit is configured as an inverting amplifier, resistors R115 and R121 scaling the sense signal down by a factor of 10. Extensive screening is employed at the amplifier's virtual ground, bootstrapped by buffers Q46 and Q41 to follow the virtual-common potential. This reduces the input capacitance, which is further compensated by feedback capacitor C60.

### 4.11.9 AC Assembly Logic and Relay Drives (Circuit Diagrams 430447 page 7.7-5)

The analog control signals are transferred into guard on the Reference Divider assembly, and latched as 'Q' outputs in the Serial/Parallel Data Converter. Offset positive logic is used:

$logic-\emptyset = -15V$ , logic-1=0V.

The signals enter the AC assembly via J7 from the Mother assembly.

M28 and M29 are inverting, open-collector Darlington drivers. The relay-drive logic places a logic-1 (OV) on the input of the selected drivers and logic- $\emptyset$  (-15V) on those not required. A selected driver operates its relay by pulling its output to -14V.

Whenever a switching command has been received, the CPU performs a control-data transfer and the UPD (IG) line from J7-53 is pulsed to logic-Ø for 50ms. Q19 is turned on, applying +15V to the relays connected to its collector. The selected relays are thus energized by 30V, but after the UPD(IG) pulse has ended Q19 turns off, and they are held on by the -12.6V between-1.4V at the cathode of D20 and-14V at the selected driver output. This method reduces the heat, generated locally by energized relay solenoids, in the relay contacts.

FETs Q42 and Q43 damp the coil of RL12 and RL13; diodes D59 and D60 isolate the parts of the printed circuit to these relays which are sensitive to power-common breakthrough, when they are deselected. D55 and D56 are overswing diodes.

### 4.11.9.1 Range Switching

(Page 7.7-5)

Range control data is input as a 3-bit code on AC RØ, AC R1 and AC R2 lines. The bit-pattern is decoded to '1 of 8' by M25, to energize the correct relays for the selected range.

In the 4200 only eight of the M25 'Q' outputs are connected. The resulting variants are listed in Table 4.11.1 against range selections.

| Function Note  1            | Range                | Range Code<br>ACR <sub>2-ø</sub> |                  |   | M25 Output Relays Energized [*=Energized] at Logic-1 |          |   |   |   |   |   |      |     |   |        |    |    |       |    |    |    |    |    |    |    |

|-----------------------------|----------------------|----------------------------------|------------------|---|------------------------------------------------------|----------|---|---|---|---|---|------|-----|---|--------|----|----|-------|----|----|----|----|----|----|----|

|                             |                      |                                  | ACR <sub>1</sub> |   | 'α'                                                  | Pin      | 2 | 3 | 4 | 5 | 6 | 7    | 8   | 9 | 10     | 11 | 12 | 13    | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| AC<br>Volts                 | 1000V                | 0                                | 0                | 0 | QØ                                                   | 3        | * |   |   |   |   |      | 5.1 |   | *      |    |    | *     |    |    | *  |    |    |    | *  |

|                             | 100V                 | 0                                | 0                | 1 | Q1                                                   | 14       | * |   |   |   |   |      |     |   | *      |    |    |       |    | *  |    | *  |    | *  |    |

| (AC FNCT at                 | 10V                  | 0                                | 1                | 0 | Q2                                                   | 2        | * | * |   |   |   |      |     |   | *      |    |    |       | *  |    |    | *  |    | *  |    |

| Logic-Ø,                    | 1V                   | 0                                | 1                | 1 | 03                                                   | . 15     | * | * |   |   |   | *    | *   |   | *      |    | *  |       |    |    |    |    |    | *  |    |

| <b>IFNCT</b>                | 100mV                | 1                                | 0                | 0 | Q4                                                   | 1        | * | * | * |   | * |      |     |   | *      | *  | *  |       |    |    |    |    |    | *  |    |

| at<br>Logic-1)              | 10mV                 | 1                                | 0                | 1 | Ω5                                                   | 6 .      | * | * | * | * |   |      |     |   | *      | *  | *  |       |    |    |    |    |    | *  |    |

|                             | 1mV                  | 1                                | 1                | 0 | Ω6                                                   | 7        | * | * |   |   |   |      |     |   | *      | *  | *  |       |    |    |    |    |    | *  |    |

|                             |                      |                                  |                  |   |                                                      |          |   |   |   |   |   | W.S. |     |   | A CONT | 11 |    | 5 5 1 |    |    |    |    |    |    |    |

|                             | Any                  | 1                                | 1                | 1 | Ω7                                                   | 4        | * | * |   |   |   |      |     |   | *      |    |    |       |    |    |    |    | *  | *  |    |

| AC<br>Current               | 100μA }              | 0                                | 1                | 1 | 03                                                   | 15       | * | * |   |   |   | *    | *   | * |        |    | *  | \     |    |    |    |    |    | *  |    |

| (AC FNCT at                 |                      |                                  |                  |   | anggapa s                                            | erone se |   |   |   |   |   |      |     |   |        |    |    |       |    |    |    |    |    |    |    |

| Logic-1,  IFNCT at Logic-Ø) | 1mA<br>10mA<br>100mA | 0                                | 1                | 0 | Q2                                                   | 2        | * | * |   |   |   |      |     | * |        |    |    |       | *  |    |    | *  |    | *  |    |

Note |1| With the 4200 operating normally: either  $\overline{\text{AC FNCT}}$  or  $\overline{\text{I FNCT}}$ , but not both, will be at logic- $\emptyset$ ; unless SAFEtY message is displayed.

TABLE 4.11.1 AC ASSEMBLY SWITCHING LOGIC

### 4.11.9.2 AC FNCT and I FNCT Logic

(Page 7.7-5)

In addition ot its primary function of controlling Voltage range switching, the AC assembly logic also needs to respond to Current range selections if Option 30 is fitted; because the AC voltage reference for the Current assembly is generated by the Voltage circuitry. For this purpose the two signals AC FNCT and I FNCT are used.

AC FNCT is at logic-Ø only when Voltage output is selected, holding M25-11 'D' input at logic-1, and energizing relays RL2 and RL10. The bit-patterns controlling the voltage range switching are shown on Table 4.11.1.

TENCT is at logic-Ø only when Current output is selected, holding M25-11 'D' input at logic-1, and energizing

relays RL2 and RL9. This connects the ACI REF lines (J7-69 to J7-72) to the ACV lines. The 10V range circuitry is used on the 100mA, 10mA and 1mA Current ranges, but the 1V range circuitry is used on the  $100\mu A$  and 1A ranges. The bit-patterns controlling the current range switching are also shown on TAble 4.11.1.

The signals AC FNCT and I FNCT are never at logic-Ø at the same time in normal operation. The only time they are at logic-1 together is when all outputs from the Control Data latches in the Reference Divider are 'Tristated'.

### 4.11.9.3 'AC Zero'

For zero output, the lines from the voltage generators to the  $\rm I+$  and  $\rm I-$  terminals are disconnected by deselection of the ranges, and a hard short is placed across the output lines by RL18.

The AC  $\rm R_{2-\emptyset}$  code is '1,1,1'. This sets M25-4 to logic-1 (energizing relays RL18) and all other M25 range

outputs to logic-Ø (the resultant bit-pattern is shown in Table 4.11.1). Thus all ranges are deselected, but relays RL2 (ACV and ACI), RL3 (Low Voltage Output), RL10 (ACV) and RL19 (1kV) remain energized). Relay RL18 connects the star-point of Common-2B (PLO) to the PHI (ACV) line.

### 4.11.9.4 'BARK DELAYED'

The 'BARK' signal does not affect the AC assembly relays. However, if the Watchdog is activated, the CPU imposes OUTPUT OFF conditions and forces the Precision DC Reference to ramp down to zero, so the PHI REF voltage also falls to zero.

All outputs from the Control Data latches in the Reference Divider are 'Tristated' by the 'BARK DELAYED' signal. This allows the pull-up resistors (AN4 and AN5) to become effective.

The  $\overline{AC}$  FNCT and  $\overline{I}$  FNCT are pulled to logic-1, and the AC R<sub>2- $\emptyset$ </sub> code is '1,1,1'. This imposes 'AC Zero' conditions on the analog sircuit, but RL2 and RL10 are also de-energized. So the DC precision reference is disconnected from the quasisinewave generator; the Sense and Power Lo lines are disconnected from the sense amplifiers.

### 4.11.10 Output Control Assembly, Logic and Relay Drives

(Circuit Diagrams 430550 Page 7.5-1)

The analog control signals are transferred into guard on the Reference Divider assembly, and latched as 'Q' outputs in the Serial/Parallel Data Converter. Offset positive logic is used:

$logic-\emptyset = -15V$ , logic-1 = 0V.

The signals enter the Output Control assembly via J5 from the Mother assembly.

The five inverters of M3 are open-collector Darlington drivers. The relay-drive logic places a logic-1 (0V) on the input of the selected drivers and logic-Ø (—15V) on those not required. A

selected driver operates its relay by pulling its output to -14V.

Whenever a switching command has been received, the CPU performs a control-data transfer and the  $\overline{\text{UPD}}$  (IG) line from J5—104 is pulsed to logic-Ø for 50ms. Q1 is turned on, applying +15V to the relays connected to its collector. The selected relays are thus energized by 30V, but after the  $\overline{\text{UPD}}$  (IG) pulse has ended Q1 turns off, and they are held on by the —12.6V between —1.4V at the cathode of D1 and —14V at the selected driver output. This method reduces the heat, generated locally by energized relay solenoids, in the relay contacts.

### 4.11.10.1 Remote Sense Logic

With Remote Sense selected, the REM SENSE signal is at logic-1. RL3 and RL4 are energized via M1-6 and M3-16 removing the shorts from across the PHI/SHI lines and PLO/SLO lines. Also, RL3-5/11 completes the circuit of PLO to the voltage output relay RL5. With Remote Sense off, RL3 and RL4 are unenergized, and their contacts are as shown (but see 4.11.10.3 below for Current ranges operation).

### 4.11.10.2 Remote Guard Logic

With Remote Guard selected, the REM GU signal is at logic-1. RL7 is energized via M1-2 and M3-13 disconnecting the internal guards and the Guard terminals from PLO. With Remote Guard not selected, the guards and terminals are connected to PLO as shown.

### 4.11.10.3 AC FNCT and I FNCT Logic

(Page 7.5-1)

In addition to its primary function of controlling the output switching, the Output Control assembly logic also needs to respond to Current function selection.

If Option 30 is fitted, the outputs from the voltage circuits need to be isolated from the output terminals. Also, because the AC voltage reference for the Current assembly is generated by the Voltage circuitry, the output/sense loop is completed in the AC assembly. Thus the local sense connections between PHI and SHI, and between PLO and SLO, are not required, and could generate noise in the loop. For this purpose the two signals AC FNCT and I FNCT are used.

AC FNCT is at logic-Ø only when Voltage output is selected, energizing relays RL5 and RL6 via M4-6 and M3-11,

providing the Output is On and the watchdog has not 'barked'. For Current ranges, AC FNCT is at logic-1, so RL5 and RL6 are unenergized as shown, breaking the lines between the voltage circuitry and the output terminals.

I FNCT is at logic-Ø only when Current output is selected, ensuring that relays RL3 and RL4 are energized, even though Remote Sense is not selected on Current ranges. This removes the local sense shorts, as though in Remote Sense.

The signals AC FNCT and I FNCT are never at logic-Ø at the same time in normal operation. The only time they are at logic-1 together is when all outputs from the Control Data latches in the Reference Divider are 'Tristated'.

### 4.11.10.4 'HIGH I LIMIT' and 'AC 1kV RANGE' Logic

The effects of these signals are described in paras 4.11.2.3 and 4.12.7.5.

### 4.11.11 High Voltage Status Detector

(Circuit Diagram 430550 Page 7.5-2)

In order to provide information to the CPU, so that it can decide whether the High/Low voltage state is as demanded, the voltage level on the PHI(ACV) line is sensed and compared against a reference.

M5 is a dual comparator whose hysteresis is set to  $\pm 0.9 V$  by D8/D9, R34/R35 and R37/R36. For as long as the voltage on the PHI(ACV) line remains within approx.  $\pm 125 V$ , the division ratio of M7 keeps the input to M5-5/9 within the  $\pm 0.9 V$  hysteresis, and M5-12/7 remains at logic-1 (approx.  $\pm 14 V$ ).

Monostable M2 is set to produce a logic-1 at its Q output (M2-7) unless its B input at M2-5 is edge-triggered negatively. In 'Low Voltage State' conditions no trigger is given, so M2-7 remains at logic-1, D4 is reverse-biased, Q2 is cut off and the  $\overline{\text{HV ST}}$  line remains at the analog control logic-1 level of 0V.

If the instantaneous PHI(ACV) voltage exceeds the  $\pm 125$ V limits (corresponding to a sinewave RMS of  $\geq 90$ V), either M5-7 or M5-12 pulls towards logic-Ø. Current source Q3 permits only 3mA to flow in M5 output circuit, so the voltage input to M2-5 (B trigger) suffers a negative-going trigger edge.

Monostable M2 produces a negative-going pulse of 130ms duration, which forward-biasses D4, Q2 conducts and the HV ST line transmits a logic-Ø pulse of 130ms duration. This is passed to the CPU, via the status register in the reference divider and the serial data interface.

The CPU has to make a decision, as to whether the programmed output voltage and the detected state are compatible. If they are not, the CPU displays 'FAIL 2', switches Output OFF, trips the watchdog and sets 'FAIL 5' display. Refer to section 2.

### 4.11.12 Overvoltage Detector

(Circuit Diagram 430550 Page 7.5-2)

An absolute limit of 1440V RMS is placed on the operation of the internal output circuitry. In order to give effect to this limit, the voltage level on the PHI(ACV) line is sensed and compared against a reference.

M6 is a dual comparator whose hysteresis is set to  $\pm 1.22 \text{V}$  by D8 and D9. For as long as the voltage on the PHI(ACV) line is less than 1440V RMS, the division ratios of M7, R26 and R25 keep the input to M6-5/9 within the  $\pm 1.22 \text{V}$  hysteresis, and M6-12/7 remains at logic-1 (approx. —1V). Q2 is cut off and the LIM DET line remains at the analog control logic- $\emptyset$  level of —15V, due to D6 being below threshold.

If the instantaneous PHI(ACV) voltage exceeds the 1440V RMS limits (corresponding to a sinewave peak of  $\pm 2025$ V), either M6-7 or M6-12 pulls towards logic-Ø. Q4 conducts, forward biassing D6 and lifting the LIM DET line to approx. -1V (analog control logic-1 level). This is passed to the  $\overline{LIM\ ST}$  logic circuitry.

Refer to Section 4.12 for subsequent action. The event is reported to the CPU via the  $\overline{\text{LIM ST}}$  logic, resulting in an 'Error OL' display,

| 111  |

|------|

|      |

| Ш    |

| 111  |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| _    |

|      |

| 11   |

|      |

|      |

| . 11 |

| la d |

|      |

|      |

| 111  |

|      |

|      |

|      |

### 4.12 HIGH VOLTAGE POWER DELIVERY

(Circuit Diagram 430450 page 7.9-1)

The AC1V signal, generated by the 1V Buffer in the Sine-Source assembly, enters the Power Amplifier as for the 10V range; but the 10V Amplifier is bypassed for the high voltage ranges.

On the 100V range, the signal is switched directly into the 100V Amplifier, where it is scaled up by a factor of 100, the amplifier output being delivered via the 'AC 10V+100V' line to the PHI (ACV) line on the AC assembly.

For the 1000V range the DC Reference is scaled in software, so that the AC1V signal Full Scale value represents

1100V output. The signal is routed through extra stages of amplification before being applied to the 100V Amplifier, whose output now drives one of two 1:6 step-up transformers (LF or HF). The power-amplifier gain on the 1000V range is controlled by feedback from the transformer secondary, into the input of the 1000V Error Amplifier. The 'AC 1kV' line transfers the transformer output to the AC assembly, where it is switched onto the PHI(ACV) line.

### 4.12.1 100V Range Power Routing

(Circuit Diagrams: 430450 pages 7.9-2 and 7.9-3; 430447 page 7.7-1)

'AC1V' enters the Power Amplifier assembly at J9-36 (page 7.9-2). Relay RL3 is un-energized, shorting the 10V Amplifier input; and RL4 is energized, routing the AC1V signal to the 100V Amplifier as '100V I/P' (page 7.9-3).

Energized relay contacts RL2-8/4 apply the signal to the Gain Stage, which provides drive to the power amplifiers in

the positive and negative heat sinks, via J3-12 and J3-11. The single-ended output from the heatsinks at J3-9 passes via R89, L7 and relay RL2-13/9, to RL3-6 (page 7.9-2), and onto the 'AC 10V+100V' line via RL4-4/8.

On the AC assembly (page 7.7-1), the signal is routed to the PHI(ACV) line as for the 10V range.

### 4.12.2 100V Power Amplifier

The 100V amplifier is in three stages:

- Gain Stage: this is similar to the first stage of the 10V amplifier, but with a different distribution of gain.

- (2) **Driver Stage:** providing most of the gain, this stage runs from a regulated 400V supply.

- (3) Buffer Output Stage: two complementary MOSFET circuits, located on the positive and negative heatsinks, provide a single-ended output with the required voltage swing, at low impedance.

The voltage gain for the whole 100V amplifier is set at 100 by the input resistors R74/R71 and the feedback resistor R88.

The 100V amplifier is also used on the 1000V range to drive the step-up transformer.

### 4.12.3 Gain and Driver Stages

(Circuit Diagram 430450 pages 7.9-2 and 7.9-3)

The AC1V signal enters the PA assembly at J9-36, passing to the input of the 100V Power Amplifier via relays

RL4-9/13 and RL2-8/4. It is referred to common 2B by developing a voltage across R72.

### 4.12.3.1 DC Offset Correction

Integrator M10 is the DC input amplifier, with diode clamping. It provides a DC input to the non-inverting input of

the AC input amplifier, M8, controlling its DC offset. This is similar to the arrangement in the 10V Amplifier.

### 4.12.3.2 AC Signal Processing

M8 is a high speed hybrid amplifier operating as an inverter. With link LKD normally made, its stage gain is approximately 2.5, frequency compensated by C18 and C72. It operates from the  $\pm\,15V$  Common-2B supplies, but its signal output is converted into a current by Q10 and Q8; allowing its mean DC voltage to reach the -400V levels required to operate the driver MOSFET output circuit. Diodes D44, D43 and D36 prevent negative latch-up.

Voltage Regulator M21 sets its pin 1 to +12V. Common-emitter buffer Q10 drives the capacitance of Q8 source-gate from the output of M8, forming a cascode current generator. The drain of p-channel MOSFET Q8 passes the signal current to the mirror Q12/Q11 at voltages close to -400V.

The current-mirror output transistor M11 is also in cascode with its associated MOSFET Q9. Emitter resistor R53 defines the current in Q9, the ratio R52/R53 setting the mirror's current gain.

MOSFETs are inherently capacitive, so measures are taken to nullify the effects, on slew rate, of the capacitive currents between Q9 electrodes. The cascode arrangement ensures that any source-gate and source-drain capacitive currents join the main flow of source current and have little effect on slew rate.

The Miller feedback of the drain-gate capacitance has the greatest effect on slew rate, generating AC currents between anti-phase electrodes which normally pass into the input circuit. In this arrangement, Q13 diverts these currents back into the cascode current, while maintaining a standing bias of about 4 volts between gate and source. Both these measures minimize the reduction of Q9 operating bandwidth.

R51 and D42 provide Q13 base bias, and D51 protects the bias curcuit. The high-power resistor R49 refers the bias circuit to Common-2, and C26 stabilizes the base-emitter bias of Q13. Zener diode D39 protects the MOSFET from source-gate voltage breakdown.

### 4.12.3.3 Driver Regulator

At Full Scale on the 100V range, the output from the driver is 200V RMS. This requires Q9 drain to provide a peak-to-peak voltage swing approaching 600 Volts, as there is no voltage gain in the heatsink power amplifiers. The positive supply which provides Q9 current therefore needs special regulation.

The 400 volt supply is at this point unregulated, so can contain line ripple and level variations, this noise level being critical to the output performance. To define a stable supply voltage, a DC restoration circuit is employed as a trough detector, maintaining a level about 5V below the most negative excursions of the ripple.

At power-up, 75V zener D57 allows a rapid charge of reservoir capacitors C49 and C59, until the charge reduces D57 voltage below the avalanche level. When D57 cuts-off, R100 provides a charge path of 1Mohm, giving a time constant of approx. 10 seconds. The smoothed voltage across C49/C59 is divided by R101, R86 and R87; so a small voltage is dropped across R101, and M20 gate is held about 5V below the +400V(2)B line voltage. The N-channel source-follower Q20 thus provides a quiet, low-impedance DC supply voltage.

Zener diodes D60 and D61 divide the voltage across C49 and C59, so that their breakdown voltages are not exceeded. The 10V zener D54 protects the TMOS gate/source from excessive voltages. D55 is included to prevent C49/C59 discharging into the 400V rail in the event of its being shorted.

The opto-coupler M16 permits the 400V supply to be switched off, allowing D56 to assume forward bias, connecting the rail to the +38V supply. This facility is not available on the 4200 AC calibrator, the 'POSITIVE' signal from the processor being permanently set to logic-1 (OV). Thus M16-6 is isolated from M16-5.

At HF, inductor L6 appears as a current source, increasing the impedance of Q9 drain load with frequency to compensate for capacitive loading. It has the advantage of not increasing the net power dissipated in the stage; any active current source would have significant output capacitance. The 12-watt resistor R65 is the main resistive drain load for Q9.

### 4.12.3.4 Driver Output

The driver develops its output voltage, which can involve peak-to-peak swings of up to 600V, across the load resistor R65. Zener diode D41 is included to clamp the output in the event of the heatsinks being disconnected. This is normally held below avalanche by the current passing through a series bias divider in the Positive Heatsink assembly, via J3-11 and J3-12.

The main frequency compensation is performed by capacitor C12. This could have been connected to the drain of Q9, but the output line slew rate is sensitive to capacitive loading. Instead it is connected via J2-7 to a low impedance point in the Negative Heatsink assembly, which follows the driver output voltage swing.

### 4.12.4 100V Buffer Output Stage

(Circuit Diagrams 430538 page 7.13-1 and 430539 page 7.13-2)

The 100V buffer output stage is split between the Positive and Negative Heatsink assemblies. The driver output voltage is connected into the Positive assembly, and the frequency compensation feedback is derived in the Negative assembly.

The whole circuit is a complementary, single-ended push-pull amplifier with unity voltage gain. To achieve the full ±300V peak voltage output, two MOSFET source-followers are connected in cascode, for each polarity, in a totempole arrangement.

To obtain the required peak current levels, each source-follower consists of two MOSFETs in parallel. In all, therefore, eight MOSFET devices are used.

On the 100V range, the output currents are such as to bias the amplifier in class A, but on the 1000V range the output currents impose class AB conditions. Crossover distortion is minimized by a regulated bias generated by a Vbe multiplier.

Power for the amplifier is provided by the same  $\pm\,400\mbox{V}$  supply that serves the driver circuit. To improve efficiency, overall power loss is reduced by regulation only where required. Thus only the driver stage is regulated, allowing the power amplifier to take power directly from the unregulated supply. Being source-followers, the 400V rail ripple is not transmitted.

### 4.12.4.1 Positive Heatsink Assembly

(Circuit Diagram 430538 Page 7.13-1)

N-channel MOSFETs Q1 and Q2 are connected in parallel, as are Q3 and Q4. All devices are matched for power dissipation and threshold voltage for an even dissipation of approx. 400W between the two heatsinks. All gate-source potentials are limited by 10V zeners.

The input voltage swing from the driver is present at J3-11 and J3-12, and the driver load current passes through resistors R18, R17 and the bias control R10. The Vgs multiplier Q5 acts as a shunt regulator, generating a bias of between 5V and 9V, set by R10. Zener diode D7 responds to the temperature of the heatsink to compensate for the temperature coefficients of the MOSFETs.

The 'DRIVE-' voltage at J3-11 is transferred directly to the negative heatsink input via J1-7 (Circuit Diagram 430539 page 7.13-2).

The 'DRIVE+' voltage at J3-12 is buffered by Q7 and applied to the gates of Q3 and Q4. In the event of an output short-circuit, Q6 detects the output current as a voltage across R14, imposing a hard limit of 1.5A by reducing the signal voltage at the input to the MOSFET gates.

The series gate resistors R5 and R6, together with their associated drain-gate capacitances, form the dominant pole of the amplifier. Damping resistor R19, with ferrite bead FB1, prevent local oscillations by emitter-follower Q7.

Q1 and Q2 act as buffers to provide a bootstrapped supply for the output devices Q3 and Q4. The gates of Q1 and Q2 are driven from the output line, obtained from the divider R16/R22/R23/R15. Capacitors C10 and C13 decouple any noise on the 400V rail; C11 and C12 correct any lag which may be generated by C10 and C13. C5 and C6 control the division ratio at HF, swamping any stray capacitance.

The drains of Q3 and Q4 are shorted together, and connected via J1-5 by a 10nF capacitor to the corresponding point in the Negative Heatsink, completing an AC bootstrap (BS). J1-4 and J1-1 are similarly linked to their corresponding points. This ensures that the AC swings in both polarities are identical.

The combined output from the Positive and Negative Heatsinks is transmitted back to the Power Amplifier assembly along the screen of the input connection.

### 4.12.4.2 Negative Heatsink Assembly

(Circuit Diagram 430538 Page 7.13-2)

This is virtually a mirror image of the positive heatsink circuit. However, because the P-channel MOSFETs are operating closer to their maximum voltage rating, they are protected by Zener diodes which limit their gate-source potentials.

The HF swamp capacitors are not required, as the whole circuit is AC-bootstrapped to corresponding points in the positive heatsink assembly, via C1, C2 and C4.

HF compensation for the driver and output stages is derived at low impedance from the junction of R2 and D12. It feeds back via J2-7 to the driver output circuit, through C12 in the Power Amplifier assembly, to avoid capacitively loading the driver output line.

### 4.12.4.3 Over-Temperature Detection

The two NTC thermistors in each heatsink circuit are part of a bridge network which detects excessive temperatures on the heatsinks. The action of the bridge is described in section 4.12.9.8.

### 4.12.4.4 100V Output Connection

DANGER For guarding purposes, the output from the heatsinks is transmitted back to J3-9 of the Power Amplifier assembly along the screen of the input cable.

> The voltages on this screen are POTENTIALLY LETHAL. Utmost caution should be exercised when working in its vicinity.

### 4.12.4.5 Heatsink Removal

The 100V Amplifier can work with the heatsinks removed, because of the clamp diode in series with the driver load. If they are removed, however, J3-9 must be connected to J3-11 to maintain the feedback. In this condition, the gain falls due to loading of the driver by the AC assembly.

### 4.12.5 1000V Range Power Routing

(Circuit Diagrams: 430450 pages 7.9-2 and 7.9-3; 430447 page 7.7-1; 430565 page 7.14-1)

'AC1V' enters the Power Amplifier assembly at J9-36 (page 7.9-2). Relay RL3 is un-energized, shorting the 10V Amplifier input; and RL1 is energized, routing the AC1V signal to the 1000V Amplifier chain.

Energized relay contacts RL1-8/4 apply the signal to the Gain X2 Stage, whose output is summed with error feedback, providing drive to the 1kV Error Amplifier.

The 1kV Error Amplifier output is passed as '1kV ERROR O/P' via relay RL1-9/13 to the 100V Amplifier (page 7.9-3). It is input through the contacts of un-energized relay RL2-6/4.

The heatsink output J3-9 is transferred directly, as the 'OUTPUT' signal, to the 1kV ENABLE relay contacts RL6-8 and RL6-9. Relay RL7 determines whether the LF or HF

transformer assembly is to be used, the OUTPUT signal being applied to the appropriate primary winding.

The secondaries of both transformers are connected into the High Voltage assembly (page 7.14-1). Relay RL2 or RL3 selects the appropriate output to be passed on to the AC assembly, via J1-28 and J1-22, as the AC 1kV signal.

The AC 1kV signal is also applied as the negative 'Error' feedback to the 1000V amplifier system. It passes through R138 and R155 on the PA assembly (pages 7.9-1 and 7.9-2), to be summed at the inverting input of M18a-2. A single net inversion is present around this loop.

On the AC assembly (page 7.7-1), the AC 1kV signal is routed by the contacts of energized relay RL20, and through fuse F2 to the PHI(ACV) line at J7-27.

### 4.12.6 1kV Power Amplifier

(Circuit Diagram 430450 page 7.9-1)

Amplification to a maximum of 1100V is in four stages:

- (1) Gain X2 Stage: the AC1V signal is HF-boosted and amplified. For the 1000V range the DC Reference is scaled in software, so that the AC1V signal Full Scale value represents 1100V output.

- (2) 1kV Error Amplifier: the Gain X2 Stage output is summed with error feedback from the secondary of the step-up transformer.

- (3) 100V Amplifier: possessing a gain of 100, the output from its heatsinks drives one of two (LF or HF) step-up transformers.

- (4) Step-up Transformer: a ratio of 1:6 allows sufficient gain in the system to provide a maximum RMS output of 1100V.

The frequency response of the amplifier is matched to the step-up transformer in use. The 'LF' signal into the amplifier is at logic-1 (OV) only when the 1kV range, and either the 100Hz or the 1kHz frequency range, is selected.

### 4.12.6.1 Gain X2 Stage

(Circuit Diagram 430450 page 7.9-2)

The AC1V signal is routed via relay RL1-8/4 to be developed across resistor R160. It is filtered by R162/C30 and applied to the non-inverting input of M15.

The feedback divider generates the X2 gain in M15; R159 and C67 providing HF lift. FET Q35 adds C68 on the

100Hz and 1kHz frequency ranges, activated by the LF signal at logic-1, to boost the lift.

Output from the X2 stage is applied to the 1kV Error Amplifier via its input resistors R156/R95.

### 4.12.6.2 1kV Error Amplifier

The input resistance to M18a is split between R156 and R95 to allow the saturation detector to reduce the gain in the event of transformer saturation.

At the inverting input of M18a the signal input is summed with the AC 1kV negative feedback signal, output from the selected transformer secondary. The resulting error is amplified by the 2 stages of M18.

On the 100kHz frequency range, the maximum voltage available from the instrument is 750V. A tapping on the HF step-up transformer secondary reduces the maximum output to this level. The signal '1kV GAIN' is therefore set to logic-Ø only on the 100kHz range, cutting off FET Q19 and restoring adequate loop gain.

The second stage, M18b, adjusts the bandpass of the amplifier to match the selected step-up transformer:

### 100Hz and 1kHz ranges:

Q26 connects C58 and R126 across the input resistor R97; relay RL5 connects C34 and R93 across the feedback resistor R92, also shorting C38 in the output line.

### 10kHz and 100kHz ranges:

Q26 connects C57 and R125 across the input resistor R97; relay RL5 connects C33 and R94 across the feedback resistor R92, and leaves C38 dominant in the output line.

These measures give the necessary loop compensation for each transformer.

When the 1000V range is selected the amplifier output is fed to the 100V Amplifier via RL1-9/13.

### 4.12.6.3 100V Amplifier

This operates as for the 100V range, and its output signal 'OUTPUT' is fed to relay RL6 contacts for application to the step-up transformer.

### 4.12.6.4 '1kV ENABLE' Relay RL6

Relay RL6 allows the OUTPUT signal from the 100V Amplifier to energize a step-up transformer, providing the following conditions are met:

The 1kV signal is at logic-Ø:

This is a processor-controlled signal, set to logic-Ø when the 4200 output is switched on, in the 1000V range.

The watchdog has not 'Barked'.

The '1kV ENABLE' switch S1 on the Power Amplifier assembly is set to 'ENABLE'. S1 is situated below the left-hand ejector lever (viewed from the front of the 4200), facing the rear of the instrument. It allows the high voltage to be switched off for servicing purposes. A red LED glows when all other conditions are met.

When RL6 is closed, the OUTPUT signal from the 100V Amplifier is switched through to the contact of RL7.

### 4.12.6.5 LF/HF Transformer Selection

Relay RL7 is activated by the 'LF' signal, applying the 100V amplifier output to the HF step-up transformer for the 10kHz and 100kHz frequency ranges, and to the LF transformer for the 100Hz and 1kHz ranges.

The two transformer are separately located, their secondaries being connected into the High Voltage assembly. The HF transformer is selected when RL7 is un-energized, its primary being returned to Common-2C. RL7 is energized to select the LF transformer, whose primary current is sensed by the Saturation Detector.

### 4.12.6.6 Saturation Detector

To obtain the required performance, the LF transformer core is constructed from a material with high remanence. It is possible for the 1kV range to be deselected when the core is magnetized, and subsequently reselected in the same sense, with resultant saturation.

The Saturation Detector circuit is activated by sensing any excess primary current in R114, associated with the loss of reactance. It progressively removes the signal input to M18b during half cycles of the appropriate sense until the core recovers, then automatically returns to its quiescent mode.

The dual amplifier M20 is biassed by R115-R118 to approximately 1V on each input. Under normal operating conditions, the unsaturated core reactance holds R114 current down, so the voltage developed across R114 is insufficient to

overcome the bias. The output from both amplifiers is of negative polarity, both diodes D58 and D59 are reverse-biassed, and FET Q18 is cut off by its gate being pulled down to -15V.

When the core saturates, the current in R114 rises rapidly and its voltage exceeds the bias on one of the detector amplifiers. One diode conducts, forcing Q18 into conduction, so the current in the transformer core is reduced to zero.

On the next half-cycle the current is reversed, so saturation is reduced. If the core saturates on successive half-cycles, they again activate the detector with further reduction. The process continues until the core remains unsaturated over the full dynamic range of the primary current, when the detector becomes inactive.

### 4.12.7 Power Supplies and Protection

Three main power supplies are employed in the Power Amplifier:

(1) ± 15V Common-2 in-guard supply. This is used for all low voltage applications, including the switching and functional logic. For the most part the logic conforms to the standard: logic-Ø= −15V; logic-1=0V.

(2) ± 38V Common-2 supply.

Required solely for the 10V Power Amplifier, this supply is generated on the separate 38V Power Supply assembly (Refer to page 7.12-1). Part of the supply circuit is situated on the Mother Assembly.

(3) ±400V Power supply.

Supplies the 100V Power Amplifier used for the

3upplies the 100V Power Amplifier used for the 100V and 1000V ranges. The line transformer secondary output is rectified and smoothed on the Mother assembly, and the main regulator circuitry for the driver stage is contained on the Power Supply / Current Heatsink. The power output stage of the 100V Amplifier receives unregulated ±400V supply. Extensive protection is incorporated.

4.12.7.1  $\pm$  38V Supply

(Circuit Diagram 430544 Page 7.12-1)

The mains (line) transformer secondary centre tap is referred to Common-2 on the Mother assembly after passing through the 38V Power Supply assembly. This secondary also provides an adjustable AC output for the 'Common Mode Null' balancing circuit.

A single bridge rectifier on the Mother assembly provides both positive and negative raw supplies for the foldback regulator in the 38V Power Supply assembly.

The 38V supply circuit is fully described in Section 4.16, para 4.16.3.4.

**4.12.7.2** ± **400V** Transformation and Rectification (Circuit Diagram 430532 Page 7.16-5)

The mains (line) transformer secondary centre tap is referred to Common-2 on the Mother assembly. The secondary is switched with the secondary for the  $\pm\,38V$  supply, to allow a lower voltage to drive the 100V power amplifier for servicing purposes. Under operational conditions in the 4200, this switch, which is situated prominently on the Mains Transformer assembly, is set to the 400V position.

A single bridge rectifier on the Mother assembly uses series diodes to achieve the high peak inverse voltage performance required for the 400V supply.

After smoothing, and part-loading by a bleeder resistor chain (the bleeder resistors also balance the voltages across the capacitors); the rectifier output is passed via J31, to provide both positive and negative raw supplies for the foldback regulator in the PS/I Heatsink assembly.

4.12.7.3  $\pm$  400V Current Control

(Circuit Diagram 430540 Page 7.13-3)

When the 400V supply is enabled, the LEDs in optoisolators M1 and M2 are conducting, allowing their optotransistors to be energized. As the circuits for both polarities are otherwise symmetrical, only the positive circuit is described.

Zener Diode D8 protects the source-gate circuit of level-shifter Q3. This N-channel MOSFET supplies a current of 1.4mA, as defined by Q8, to the current-monitor reference zener diode D7. This current is available only if the 400V supply is enabled by M1, otherwise Q4 base is pulled down by D1/R9, Q4 conducts via D7 and Q9 is pinched off.

Under normal conditions the Power Amplifier supply current is drawn through the P-channel MOSFET Q9, which is held in conduction by R8, R12 and D2. The current is sensed by the parallel combination of resistors R17 and R32. Although the peaks of the current taken by the power amplifier can reach 1.4A, the mean value is less than 0.5A. Ripple currents making up the difference are smoothed by the main reservoir capacitors C31 and C22 on the Power Amplifier assembly.

For mean currents more than approximately 0.5A (in particular for output short-circuits); the voltage sensed across R17/R32, subsequently divided by the attenuator R10/R9, exceeds the threshold of Q4/D7. Q4 conducts to pass current into R8, reducing the drive to Q9 gate, so the  $\pm$ 400V(2)B voltage at D5 anode falls. When the voltage dropped by Q9 reaches 56V, zener D5 conducts and pulls Q4 base down, further reducing the drive to Q9 gate. This cumulative action is slowed only by the time constant of the combination R34/C15, so that both voltage and current on the  $\pm$ 400V(2)B line are simultaneously closed down.

With a persistent 400V overload, the circuit cannot recover naturally from this 'foldback' mode. However, the 400V voltage is monitored. If the 400V monitor senses a failure, a status bit is passed back to the CPU via the SSDA serial link. The CPU makes three attempts to reinstate correct operation by removing the PA bias while restarting the supply via the 400V enable line. If after the third attempt the voltage does not recover, the CPU assumes that a hardware fault is present, so displays the 'FAIL 7' message.

### 4.12.7.4 100V Overload Detector

(Circuit Diagram 430450 Page 7.9-6)

The  $\pm 400 \text{V}(2) \text{B}$  lines enter the Power Amplifier assembly from the PS/I Heatsink at J1-8/6 and are filtered by L1 and L2 before being applied across two neon lamps LP1 and LP3. These lamps are visible from the top and rear of the instrument when the PA board is exposed, indicating that a dangerous voltage is present.

The 400V(2)B lines continue on to power the driver stage of the 100V amplifier, where the voltage is regulated as described in sect 4.12.3.3.

The  $\pm 400 \text{V}(2) \text{C}$  lines supply the power amplifier in the Positive and Negative Heatsinks. On the 100V range, the current in each of these lines is used as an analog of the load placed on the amplifier. (On the 1000V range, any overload is sensed by a series detector in the OUTPUT control assembly.)

The '100V A' line is set to logic-1 (OV) only when the 100V range is selected ('100V D' is not used in the 4200). Driver Q7 pinches off the two FET switches Q6 and Q37, removing the shorts from R37 and R21, thus allowing the overload detector to operate. In normal use, links LK B and LK C are not connected. Their test purpose is to allow the current mirrors Q1 and Q3 to be powered without the level-shifters Q2 and Q4.

Most of the positive output current for the heatsinks passes through the series combination of R34 and D27, the negative currents through R9 and D4. As the both positive and negative circuits are symmetrical, only the positive circuit is described.

Current mirror Q3 diverts approx. 1.8% of the positive supply current into the level-shifter Q4, R36 and into the common resistor R37. Similarly Q1 draws current out of R37. Under no terminal load conditions these two currents are balanced, even if the output voltage is high.

Any AC output load current from the power amplifier is reflected by ripple currents in both positive and negative supplies. The net instantaneous current flowing in R37 alternates in synchronism with the output cycles, its amplitude increasing as the load current increases. So the amplitude of the alternating voltage across R37 is an analog of the output load current, and can be compared against a scaled reference voltage.

A window comparator is formed from the two halves of M2 and the voltage across R37 is applied to both halves. The outputs at M2-12 and M2-7 are uncommitted. Each half is biassed by approx. 1.025V in the correct polarity, so that unless any voltage peak across R37 exceeds this level, both M2 outputs will be pulled to OV by R21. So Q9 remains cutoff

Any peak greater than 1.025V ovrcomes the bias on one half, causing its output to fall to -15V, so Q5 conducts, lifting TP2 to 0V (logic-1). Diode D13 is part of a wired-OR gate which then sets the limit detector latch M5a (page 7.12-5), resulting in the LIM ST status bit being set to logic-1. This is passed to the CPU via the SSDA serial link. Meanwhile the LIM DET signal passes via D38, becoming the 'I LIM 100V AMP' signal to Q14 (page 7.12-3) in the gain stage of the 100V amplifier. Q14 conducts, shorting the input to the amplifier to Common-2, and reducing the amplifier output.

The CPU tries to toggle the latch, and will succeed once the overload is removed. While it is clocking the toggle with 'I LIM RST', it displays the message 'Error OL'. Note that the action described trips the output off. Thus removing a terminal overload will not restore the output.

### 4.12.7.5 1000V Overload Detector

(Circuit Diagram 430550 Page 7.5-1)

For the 1000V range, so as to protect the step-up transformers, overloads are detected directly in the output lines to the terminals. For this range only, two resistors are inserted in the PHI(V) line in the Output Control assembly. The voltage across the resistor is rectified and compared against a reference. If the voltage is excessive, the comparator generates a LIM DET signal.

The 'AC 1kV RANGE' signal enters at J5-102. This is at logic-1 to energize relay RL1, only if the 1000V range is selected. RL1 removes the short from R31 and R32.

The 'HIGH I LIMIT' signal enters at J5-98. When the 1000V range is selected, this is at logic-1 only for the 10kHz, 100kHz and 1MHz frequency ranges. It energizes relay RL2, shorting R32, so that higher currents are required to trip the

LIM DET signal. As frequency increases, so do the currents taken by the capacitance of the internal tracking and wiring; R31 is compensated by C16 to bypass this capacitive loading.

A diode-bridge rectifies the voltage developed across the selected resistor(s). The voltage is limited to 10V by D14, and resistor R33 sets the trip current level for the opto-isolator M8.

The isolator operates from the 5 volts between -10V and -15V. In normal operation M8 output at M8-6 is open-collector so Q5 does not conduct. When the output current is sufficient to trip M8, Q5 emitter is pulled low and so Q5 conducts, its collector current being drawn through R21 and R20 (page 7.5-2). Q4 is switched on, setting the LIM DET line to logic-1.

### 4.12.8 PA Power Supply Monitors

(Circuit Diagram 430450 Page 7.9-4)

All three power supply voltages: 15V, 38V and 400V; are monitored using three virtually identical comparators to initiate individual 'FAIL' messages. In addition, if either the 400V or the 15V circuit detects a low power

supply voltage, the 400V supply is disabled. Because the monitors are so similar, only the 400V circuit is fully described.

### 4.12.8.1 400V Monitor

Zener diode D5 is the 2.45V reference for all three comparators. It is ballasted by R30, and its  $\pm 2.45$ V is applied to the non-inverting input of M3d. Its voltage is divided equally by two sections of AN3, applying  $\pm 1.23$ V to the inverting input of M3a.

The +400V(2)B line voltage is divided down to approximately 3.25V by R3 and R16, and applied to the inverting input of M3d. This is sufficient to hold M3d-14 output negative. Diode D20 is held below threshold by R7 and a 1Mohm pull-up on the 400V(2) status line in the Reference Divider. If the +400V line voltage falls to 300V, M3d output goes positive, limited by D6. D20 conducts, setting the status line to logic-1 (0V), positively limited by D8.

The -400V(2)B line voltage is similarly divided down to approximately +0.9V by R4 and R26, and applied to the non-inverting input of M3a. This is sufficient to hold M3a-1 output negative. Diode D23 is also held below threshold. If the -400V line voltage falls to -315V, M3a output goes positive, limited by D7. D23 conducts, again setting the status line to logic-1 (0V).

The output line gives an input to the 400V enable logic (sect 4.12.9.4).

In normal 400V operation R31 is shorted by the 400V/50V switch on the Mains (line) transformer. When this is set to 50V, the 'Lo SUPPLY A' line is connected to -15V, effectively disabling the monitor output by holding the 400V(2) line at logic- $\emptyset$ .

### 4.12.8.2 38V Monitor

The thresholds for operation of the 38V fail flag are: +32V and -33V. Otherwise the action is the same as the 400V monitor.

### 4.12.8.3 15V Monitor

The thresholds for operation of the 15V fail flag are:  $\pm 12.05$ V and  $\pm 12.3$ V. The action is similar to the 400V monitor, but because the 15V circuit is running from the supply it is monitoring, extra precautions are required and the action is slightly modified.

Under normal operating conditions, D21 and D22 are reverse-biased, so the 15V(2) FAIL line is pulled to logic- $\emptyset$  by R17.

If the -15V supply fails, the action is as before, but in this case it is assisted by M3 power supply being between +15V and 0V. D22 will conduct to drive the 15V(2) FAIL line to logic-1.

On the other hand, if the +15V supply fails, the reference supply to D5 would collapse and both amplifiers would run between OV and -15V (D32, shown on page 7.9-6, prevents the +15V line reversing). The 2V zener D16 then ensures that as the +15V supply collapses, M3c-9 is pulled more negative than M3c-10 at all times, regardless of supply levels. Thus M3c-8 output is driven to its positive rail, which can source enough current to hold the 15V(2) FAIL line at logic-1.

The 15V monitor output line also gives an input to the 400V enable logic (sect 4.12.9.4).

### 4.12.9 PA Logic and Relay Drives

(Circuit Diagrams 430450 Pages 7.9-4 and 7.9-5)

The CMOS logic operates between 0V and -15V, with logic-1=0V, and logic- $\emptyset$ =-15V. Relays are tied to +15V on one side, and controlled on the other by the uncommitted collector of an inverting Darlington driver. Thus when the

input to the driver is logic-1, the relay is energized by  $\pm$  15V; and when the driver input is logic-Ø, its output is high impedance, releasing the relay.

### 4.12.9.1 Range Switching

(Page 7.9-5)

In the 4200, the inputs to decoder M7a are not connected outside the PA assembly. They are therefore all pulled to logic-1 by AN4, including the 'E' input, so all 'Q' outputs are at logic-Ø.

The three inputs AC RØ, AC R1, AC R2; carry the range switching information, and are decoded by M7b as follows:

|                                      | N                     | 17b outpu        | N                     | /17b inpu             | its                   |                  |

|--------------------------------------|-----------------------|------------------|-----------------------|-----------------------|-----------------------|------------------|

|                                      | Q2                    | Q1               | QØ                    | E                     | В                     | Α                |

| Range<br>Select                      | AC R2                 | AC R1            | AC RØ                 |                       |                       |                  |

| 1000V<br>100V.<br>10V<br>1V<br>100mV | Ø<br>Ø<br>Ø<br>Ø<br>1 | Ø<br>Ø<br>1<br>1 | Ø<br>1<br>Ø<br>1<br>Ø | Ø<br>Ø<br>1<br>Ø<br>Ø | Ø<br>1<br>Ø<br>Ø<br>Ø | 1<br>Ø<br>Ø<br>Ø |

| 10mV<br>1mV                          | 1                     | Ø<br>1           | 1<br>Ø                | Ø                     | Ø<br>Ø                | Ø<br>Ø           |

### 10V Range Logic

The input to Q6-1 is always logic-1. On the 10V range only, the input to Q6-2 is logic-Ø, giving logic-1 at M6-3. Thus relay RL3 operates only when the 10V range is selected.

### 100V Range Logic

The input to Q12-8 is logic-Ø only when the 10V range is not selected, and the input to Q12-9 is logic-Ø only on the 100V range. This gives logic-1 at M12-10, so relay RL2 operates only when the 100V range is selected.

### 1000V Range Logic

The input to Q13-4 is logic-Ø only when the 1000V range is selected, so relay RL1 operates only when the 1000V range is selected. An 'AC 1kV RANGE' signal is also passed to the Output Control assembly to select the overload sense resistor.

### 4.12.9.2 Range-Changing Logic

In the 4200, the input to M12-13 is held permanently at logic-Ø. Except during range changes, the AC FNCT and I FNCT signals are always of opposite logic. Although M7a-4 is

always at logic-Ø, the logic-1 from M6-11 is sufficient to energize relay RL4. During range changes both function signals are driven to logic-1, momentarily releasing RL4.

### 4.12.9.3 1kV Enable Logic

With the 1000V range selected, and if the watchdog has not 'barked', M12-3 is at logic-1 and LED D70 is lit. Relay RL6 is energized if the 1kV ENABLE switch on the PA assembly is set to ENABLE.

For other ranges, or if the watchdog barks, RL6 is deenergized, removing the AC drive to the step-up transformers. LED D70 is also de-energized.

### 4.12.9.4 '400V ENABLE' Logic

The '400V(2) OFF' signal from the CPU is normally at logic-Ø for voltage ranges; but after a 'FAIL 7' message indicates a 400V supply failure, it is toggled three times, attempting to restore the supply.

In normal operation, therefore, with BARK at logic-Ø, the PS1 OFF signal from M11-4 is also at logic-Ø, and is input to M1-1/6 (page 7.9-4). M1 consists of six inverting drivers, each with uncommitted-collector output (as used for the relay drivers). M1-1 at logic-Ø allows M1-2 to be pulled to logic-1 by AN1-1/2, or to logic-Ø by M1-14. In the lower chain with four inversions, M1-14 is also open-collector, if a 400V or 15V failure has not been detected by the monitors.

Thus for normal operation M1-2 is pulled to logic-1 and the 'ENABLE 400V-' line from M1-15 is held at logic-Ø (-15V). With the 'ENABLE 400V+' line it energizes the optoisolator LEDs in the 400V power supply (PS/I heatsink page 7.13-3).

A failure of either the 400V or 15V supply pulls M1-3 to logic-1, disabling the 400V supply by setting the ENABLE 400V— line to logic-1. If the  $\pm$ 15V or  $\pm$ 15V rail collapses, the opto-isolator current is cut off in any case, due to zener D24.

### 4.12.9.5 'BIAS OFF' Logic

On the 100V or 1000V ranges, after receiving a 400V FAIL signal from the monitor, the CPU attempts three times to restore the 400V supply. The foldback current limiting for the supply (in the PS/I heatsink) prevents reinstatement if an overload persists. Thus it is necessary to remove the overload if the supply is to be restored. This is done by setting the BIAS OFF line to logic-Ø (-15V), cutting off Q10 (page 7.9-3) and removing the output drive.

The attempts are made by toggling the 400V (2) OFF line (described in sect 4.12.9.4). Each time the supply is enabled, R6 and C1 hold the BIAS OFF signal at logic-Ø for about 1ms to allow the supply to build up before the load is reapplied.

After three unsuccessful attempts, the CPU assumes a permanent hardware fault and holds the  $400V\ (2)$  OFF signal at logic-1.

### 4.12.9.6 'LIM ST' Logic

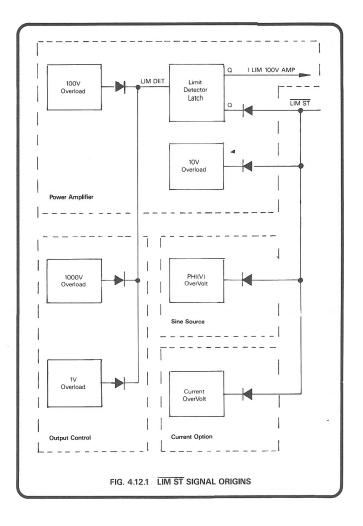

This status signal is passed back to the CPU via the SSDA serial link to indicate that certain limits have been exceeded. The LIM ST signal entering the Reference Divider assembly at J4-76 (page 7.4-6) can be activated to logic-Ø by any one of six detectors, as illustrated in the simplified diagram of Fig. 4.12.1.

The signal output from the Power Amplifier at J9-67 (page 7.9-2) can result from the LIM DET signal setting the latch M5a (page 7.9-5).

LIM DET is set to logic-1 by the 100V Overload Detector (page 7.9-6), if the 400V supply current peaks are excessive. It can also be set by the 1000V Overload Detector or Overvoltage Detector in the Output Control assembly (page 7.5-1/2). The logic-1 is immediately transferred via D38 as 'I LIM 100V AMP' to the gate of Q14 (page 7.9-3). Q14 conduction reduces the 100V amplifier input to zero, so if the overload is external the LIM DET signal should rever to logic-Ø.

The latch M5a is set by logic-1 on pin 6, for as long as LIM DET remains at logic-1. Its 'Q' output reinforces and latches the 'I LIM 100V AMP' signal. Its 'Q' output is the 'LIM ST' signal, so the CPU is informed. The CPU initiates a series of clock pulses on the 'I LIM RST' line via the SSDA and Reference Divider, so that M5a can be reset as soon as the LIM DET signal clears to logic-Ø, M5a 'D' input being strapped to -15V. The CPU also displays the 'Error OL' message.

If the LIM DET line has cleared to logic-Ø, the 100V Amplifier input is reinstated by M5a being reset. Furthermore, if the overload was temporary, the LIM DET line remains at logic-Ø, and operation returns to normal. The CPU is informed by LIM ST at logic-1, so the reset pulses are discontinued, and the Error message is removed.

For a persistent overload, the detectors operate once again. The cycle repeats until other user action is taken to remove the overload. The Error message continues to be displayed.

If the overload is an internal fault, it is likely that another protection circuit will have detected it and taken its own action.

### 4.12.9.7 'LF', 'LF' and '1kV GAIN'

These are signals used to control the gain and compensation of the 1kV amplifiers (Refer to section 4.12.6).

The 'LF' signal is set to logic-1 by the CPU via the SSDA serial link and Reference Divider latches, when the 1000V range and the 100Hz or 1kHz frequency ranges are selected. It is inverted as 'LF' at M11-12, and subsequently inverted as buffered 'LF' at M11-10.

'FREQ RØ' is also CPU-controlled. It is set to logic-1 when either the 1kHz or 100kHz frequency range is selected.

'LF' and 'FREQ RØ' are combined at M6-10 to give the '1kV GAIN' signal, which is at logic-Ø only when the 100kHz range is selected. (The software prevents the 1MHz range being selected on the 1000V range).

### 4.12.9.8 Thermistor Comparator